#### BEE 271 Digital circuits and systems Spring 2017 Lecture 10: Sequential circuits

Nicole Hamilton https://faculty.washington.edu/kd1uj

# Topics

1. Introduction to sequential circuits

### Chapter 5

## Flip-Flops, Registers, and Counters

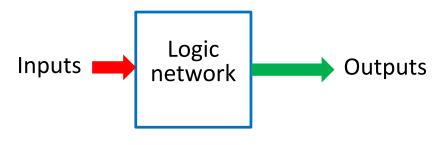

#### Combinatorial vs. Sequential Logic

Combinatorial or combinational logic

- 1. No memory elements.

- 2. No feedback from the outputs to the inputs.

- 3. Outputs depend only on the inputs.

Sequential logic

- 1. Contains memory that can remember a present state.

- 2. Outputs feed back to the inputs.

- 3. Outputs depend on both inputs and the present state.

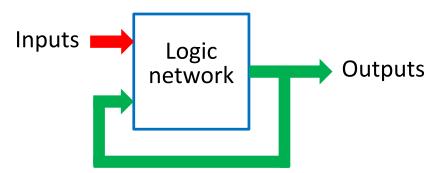

# Two problems

- 1. Would like to save state, e.g., count things.

- 2. Need to wait until signals settle

#### Figure 5.1. Control of an alarm system.

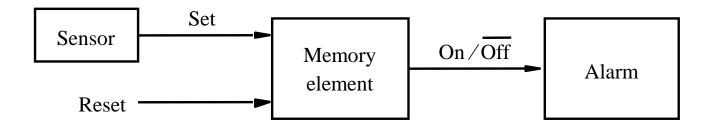

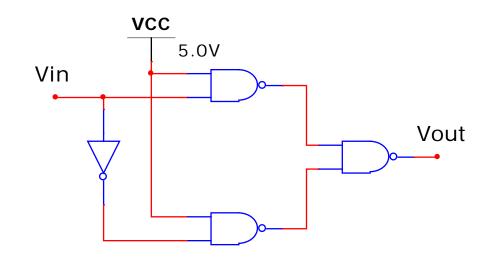

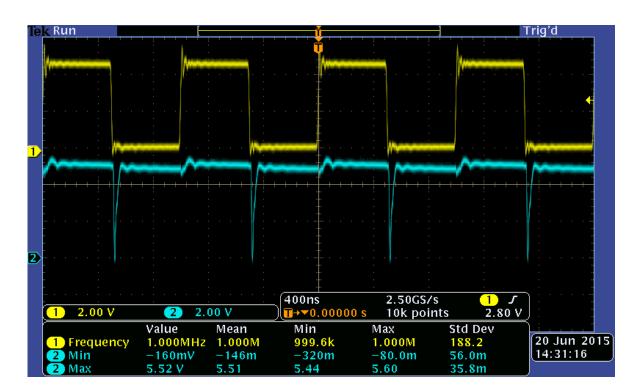

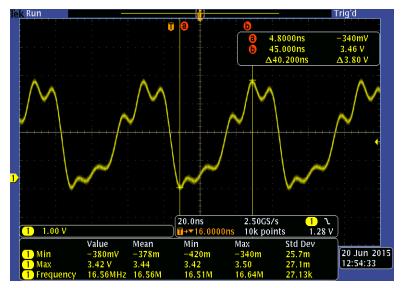

Real gates have propagation and rise and fall times.

Causes hazards where outputs change when they shouldn't.

Must wait until signals have settled.

# A circuit with a hazard in lab 1.

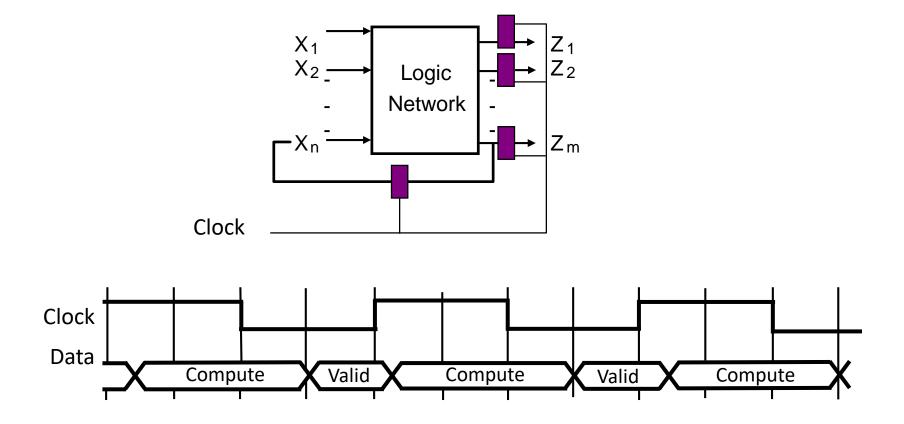

#### Safe Sequential Circuits

Clocked elements on feedback, perhaps outputs Clock signal synchronizes operation Clocked elements hide glitches/hazards

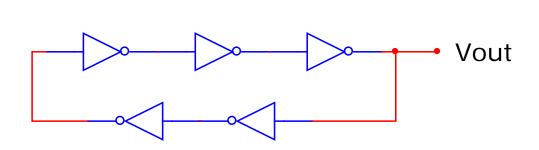

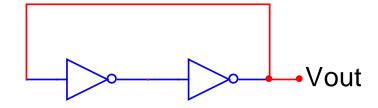

# Feedback

Ring oscillator with an odd number of inverters

Bistable latch with an even number of inverters

Vout can be either 1 or 0 but whatever it is will be stable.

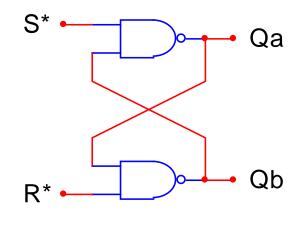

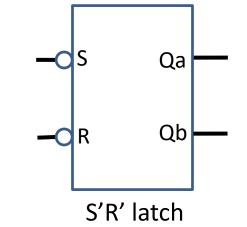

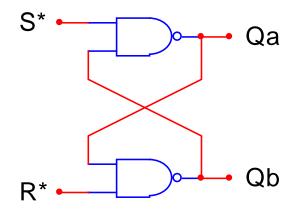

#### Set/reset latches

|   | S* | <b>R</b> * | Qa        | Qb        |

|---|----|------------|-----------|-----------|

|   | 0  | 0          | 1         | 1         |

| _ | 0  | 1          | 1         | 0         |

|   | 1  | 1          | no change | no change |

|   | 1  | 0          | 0         | 1         |

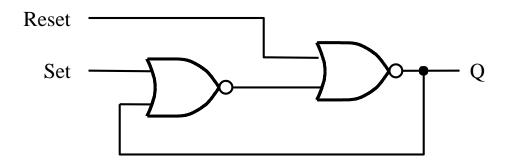

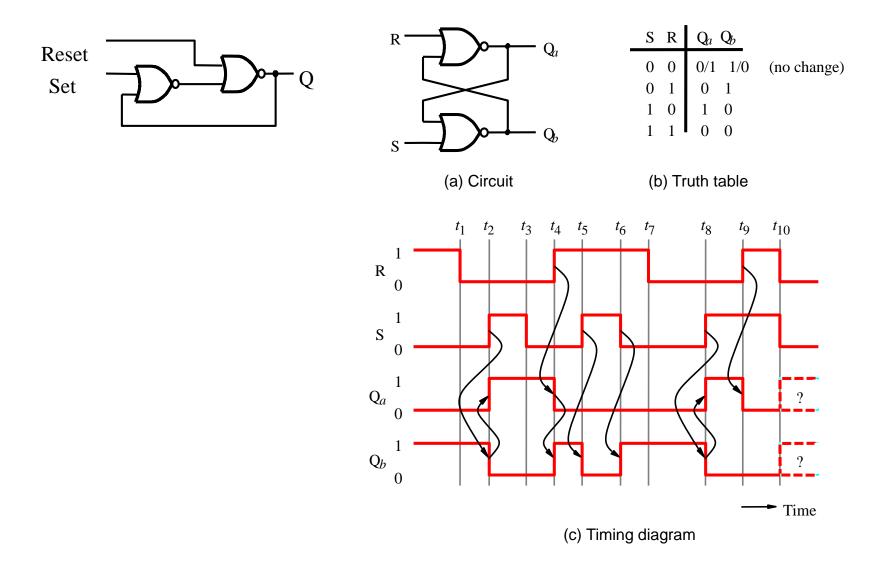

Figure 5.3. A memory element with NOR gates.

Figure 5.4. A basic latch built with NOR gates.

####

nor ( Qn, set, Q ); nor ( Q, reset, Qn );

#### endmodule

nand ( Q, setn, Qn ); nand ( Qn, resetn, Q );

```

module SRLatch( input s, r, output reg Q );

```

```

always @( * )

casex ( { s, r } )

'b1x: Q = 1;

'b01: Q = 0;

endcase

```

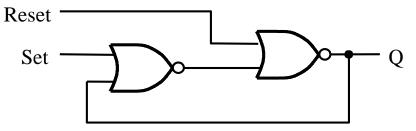

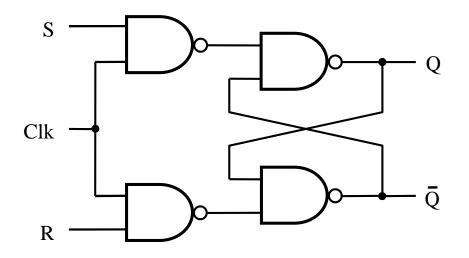

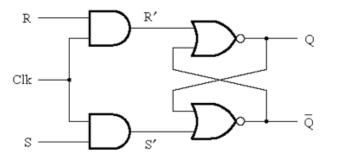

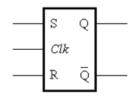

Figure 5.6. Gated SR latch with NAND gates.

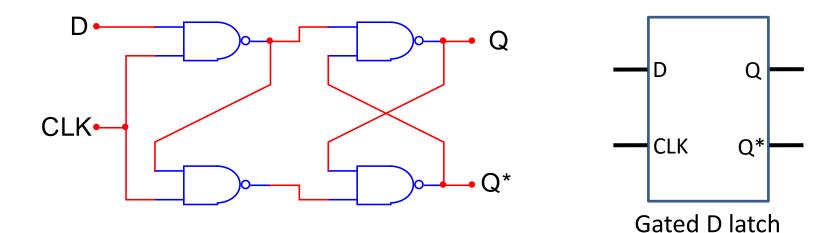

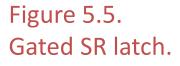

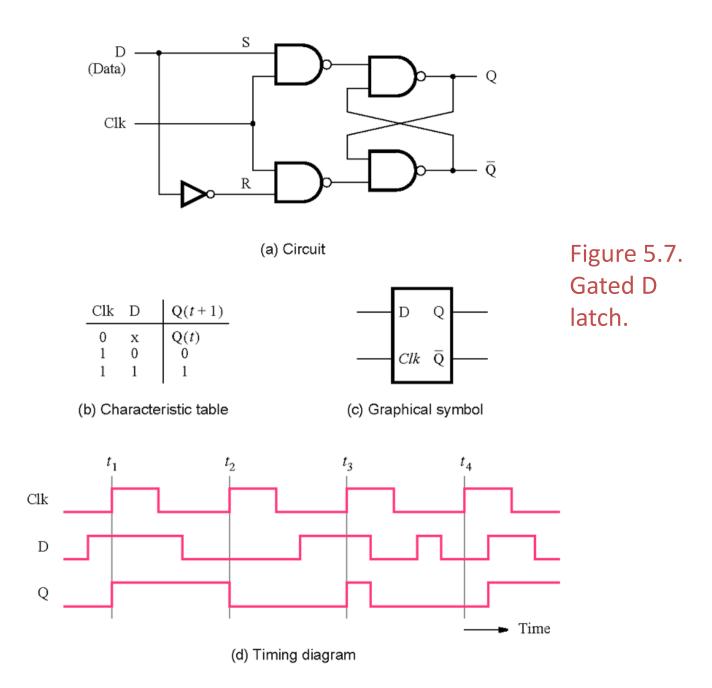

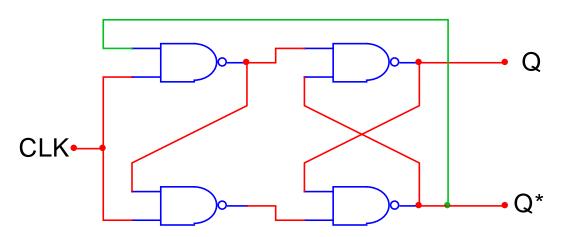

## Gated latches

Clock used to sample the input when the clock is high and hold it when the clock is low.

clock = 10 KHz / D = 52 KHz

```

module DLatch2( input clock, D, output reg Q );

always @( * )

Q = clock ? D : Q;

endmodule

```

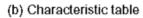

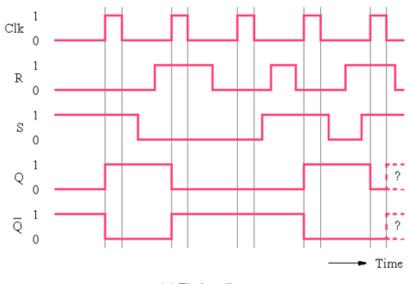

| Clk | S | R | Q( <i>t</i> + 1) |

|-----|---|---|------------------|

| 0   | x | x | Q(t) (no change) |

| 1   | 0 | 0 | Q(t) (no change) |

| 1   | 0 | 1 | 0                |

| 1   | 1 | 0 | 1                |

| 1   | 1 | 1 | x                |

|     |   |   | I                |

(a) Circuit

(c) Timing diagram

(d) Graphical symbol

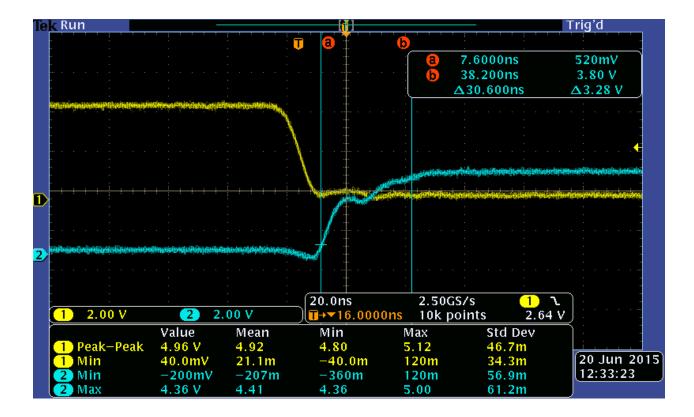

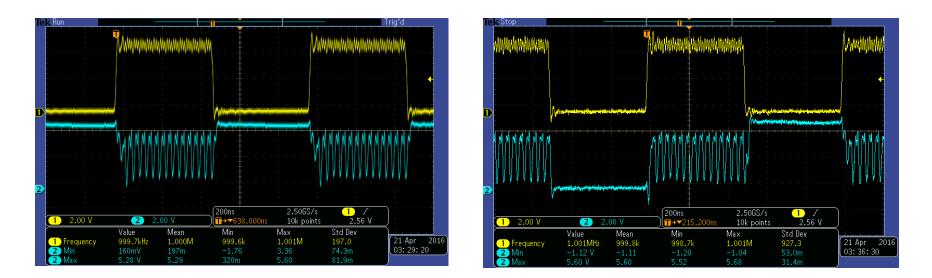

# Flip Flops

Problem: latches are sensitive to any changes that occur with the input while the clock or control signal is high

– Glitches/Hazards

- Unsynchronized changes

- Solution: use flip-flops, devices that react only on the clock edge

But we cannot build reliable counters or anything else requiring feedback with latches.

What you get depends on small differences in the length of the green wire.

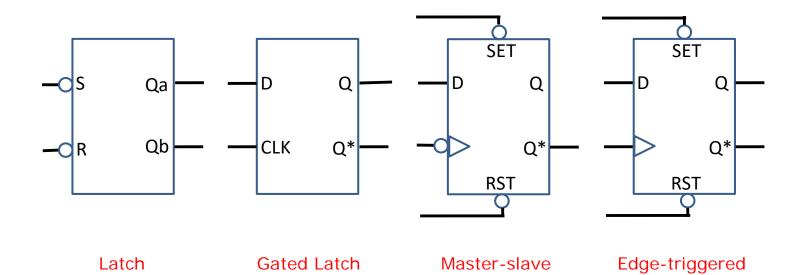

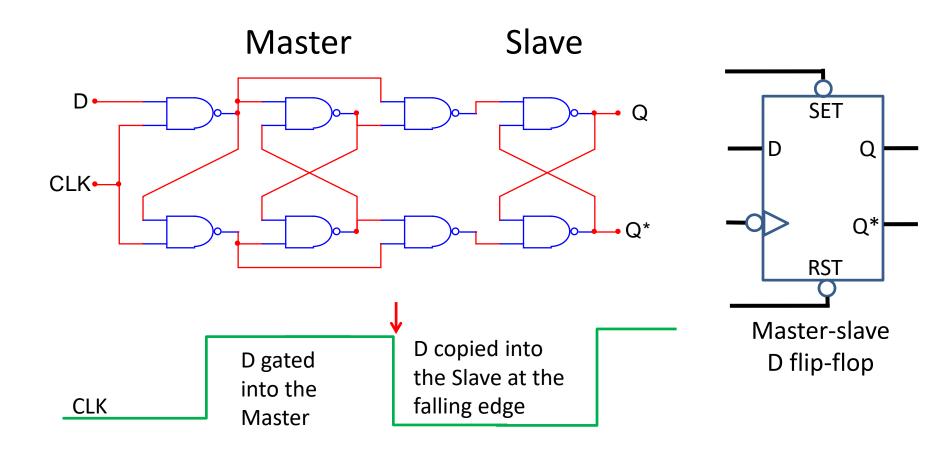

#### Solution is to isolate inputs from outputs

Three popular alternatives:

- 1. Two-phase clocking

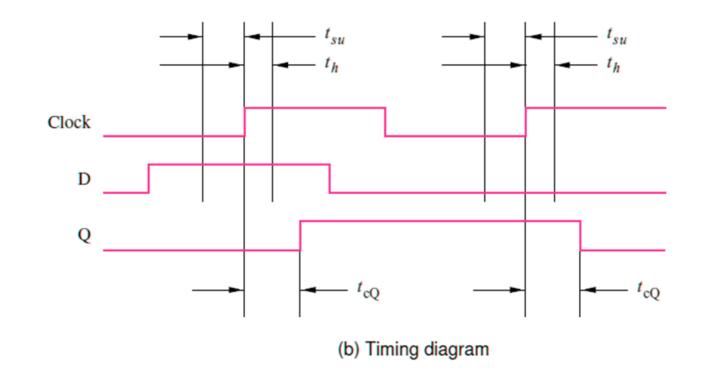

- 2. Master-slave

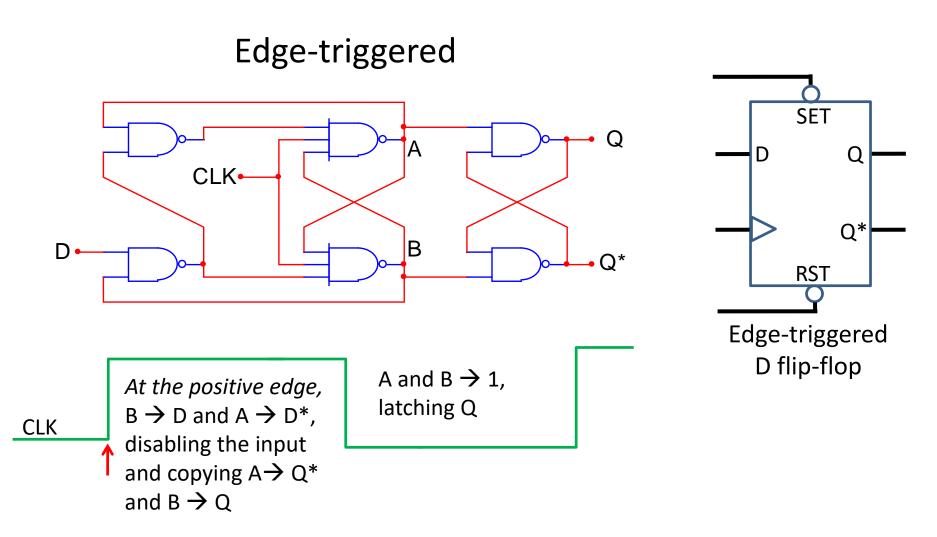

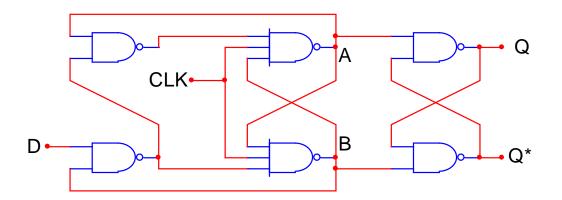

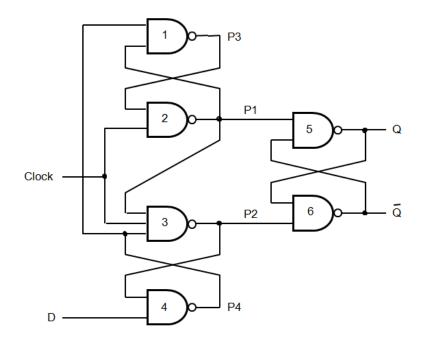

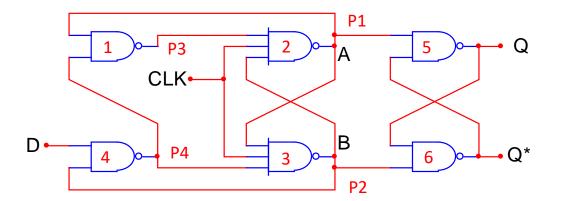

- 3. Edge-triggered

### Terminology

*Basic latch:* A feedback connection of two NORs or two NANDs that can store 1 bit. Set using the S input and reset using the R input.

*Gated latch:* A basic latch that includes input gating and a control input signal. Retains its value when the control signal is 0, changes state when the control signal is 1.

*Flip-flop:* A storage element whose output changes only on the edge of a controlling clock. Can be either positive or negative edge-triggered.

#### Two-phase clock

Non-overlapping clocks for phases 1 and 2. Advantages are fewer gates per bit and that you can put logic between both phases so long phase 1 latches only use phase 2 inputs and vice versa.

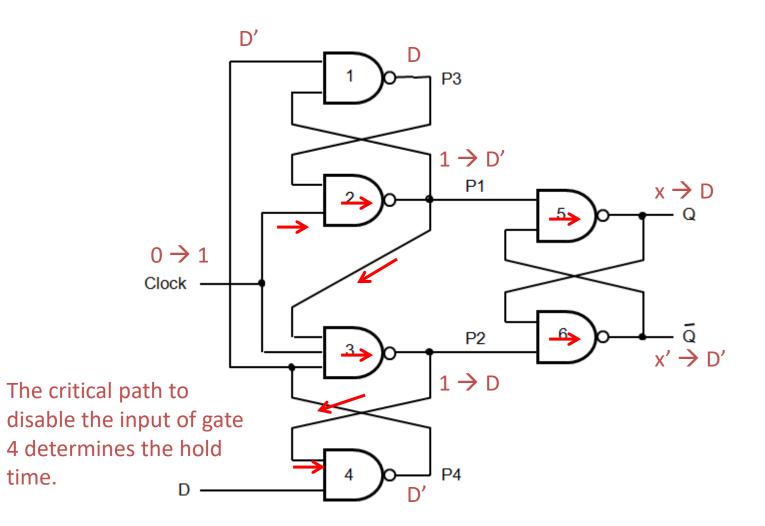

Because of the signal path is longer to the slave, we can guarantee the input to the master will be disabled before the input to the slave is enabled.

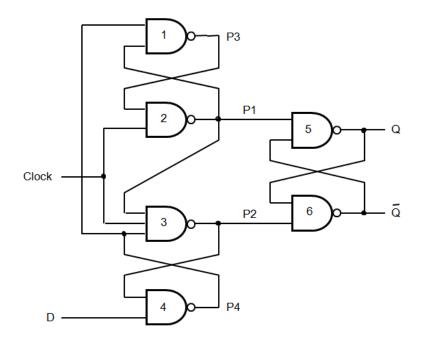

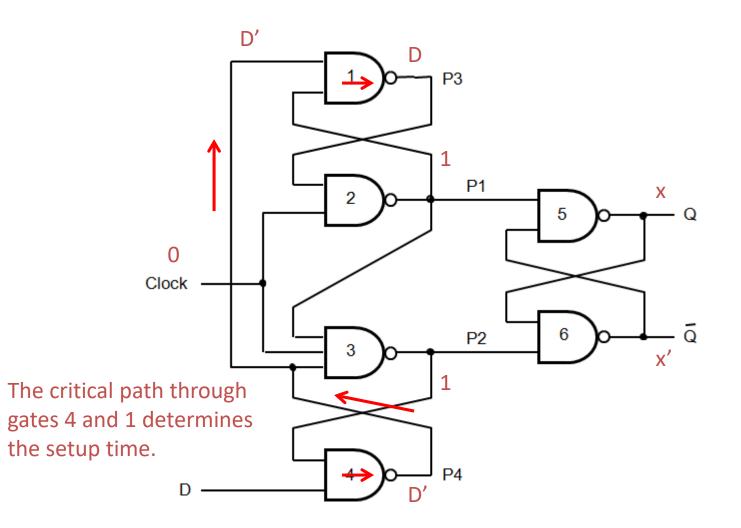

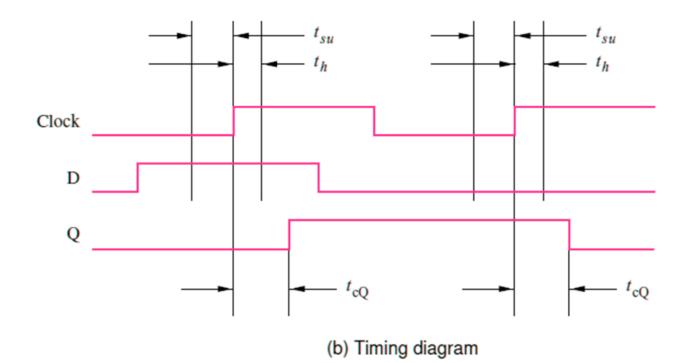

Requires a hold time: D is not allowed to change until the rising edge of the clock has propagated through A or B back to the input NANDs, latching whichever side was a zero.

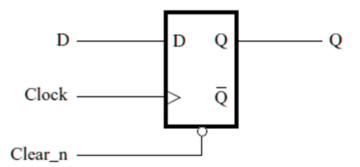

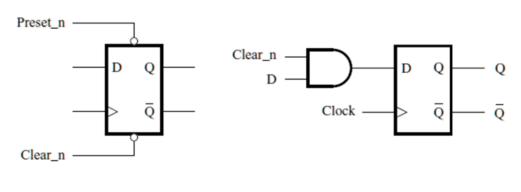

(a) D flip-flop with asynchronous clear

t<sub>su</sub> + t<sub>h</sub> is called the "aperture" or "window" when the input must be good.

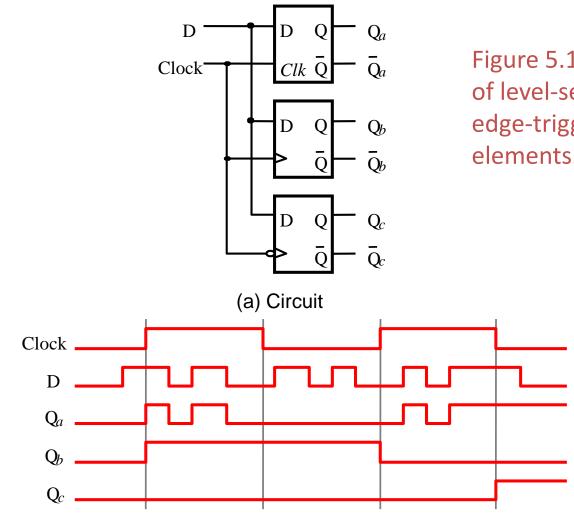

Figure 5.10. Comparison of level-sensitive and edge-triggered D storage elements.

(b) Timing diagram

module DMasterSlave1( input clock, D, output reg Q );

```

wire Qm;

DLatch1 master ( clock, D, Qm );

DLatch1 slave ( ~clock, Qm, Q );

```

endmodule

module DMasterSlave2( input clock, D, output reg Q );

```

reg Qm;

always @( * )

if ( clock )

Qm = D;

else

Q = Qm;

```

module DMasterSlave3( input clock, D, output reg Q );

```

reg Qm;

always @( negedge clock )

Q <= D;</pre>

```

module DMasterSlave3( input clock, D, output reg Q );

```

reg Qm;

always @( negedge clock )

Q <= D;</pre>

```

endmodule

module DEdgeTriggered( input clock, D, output reg Q );

```

always @( posedge clock )

Q <= D;</pre>

```

(b) Graphical symbol

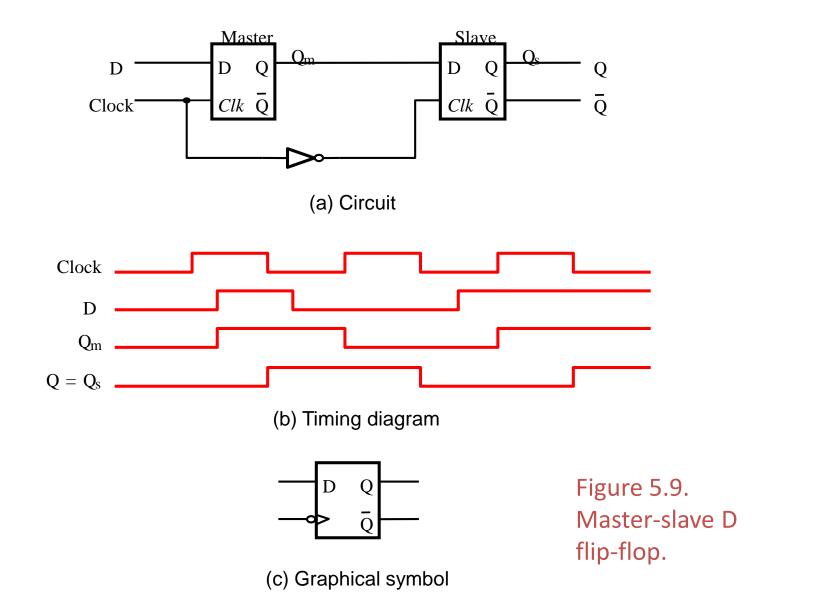

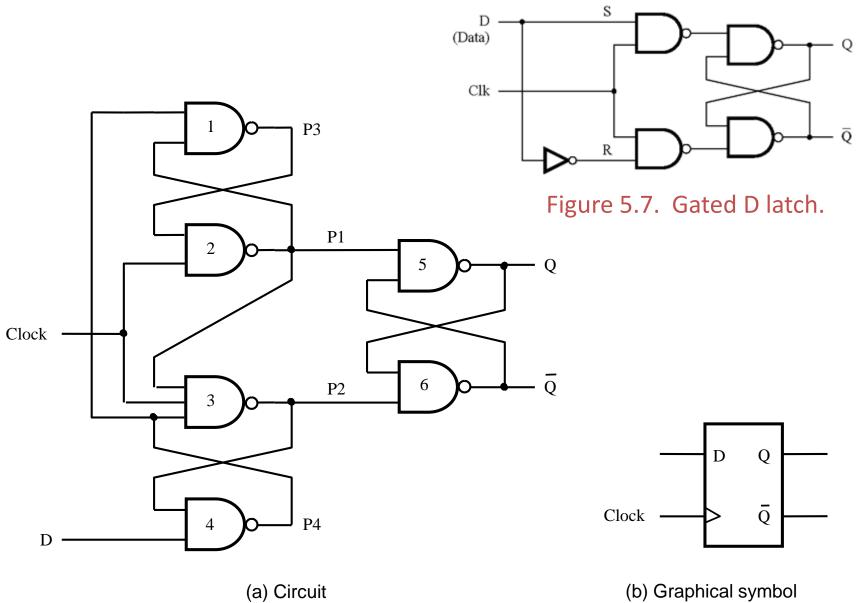

Figure 5.11. A positive-edge-triggered D flip-flop.

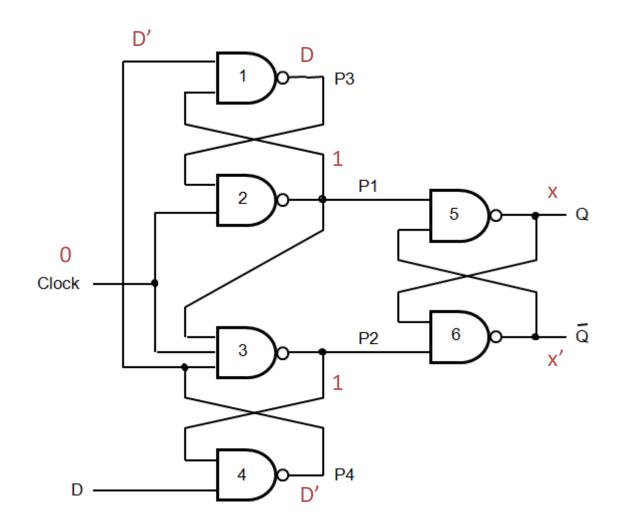

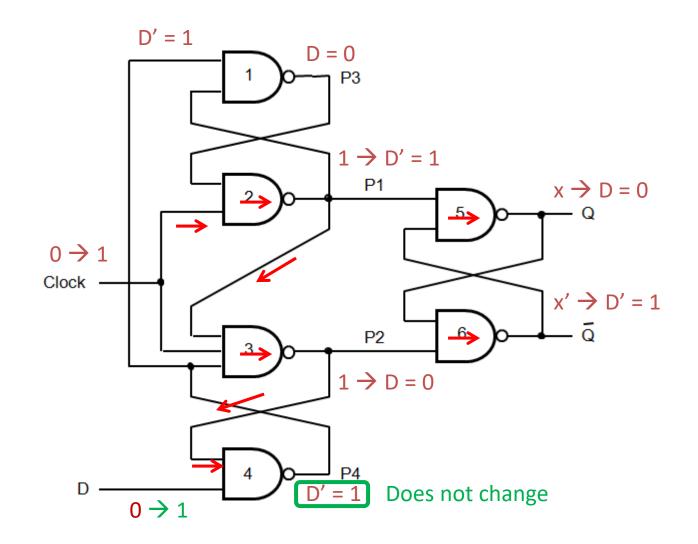

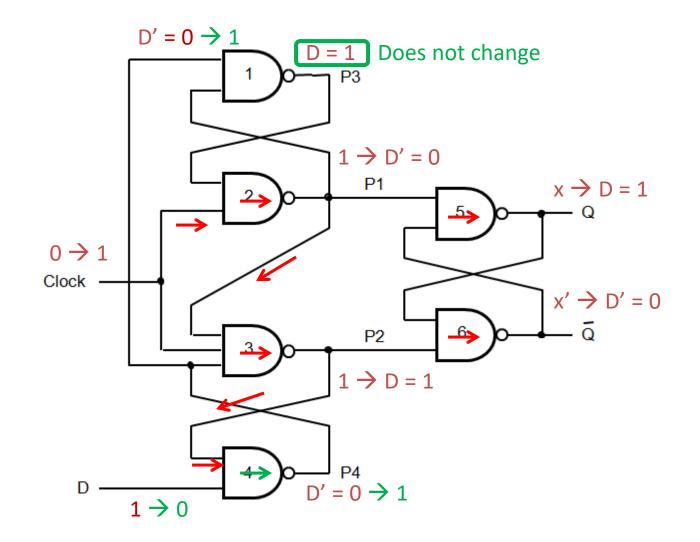

Steady-state clock = 0.

Steady-state clock = 0.

Clock transition 0  $\rightarrow$  1

D transitions  $0 \rightarrow 1$  after the hold time

D transitions  $1 \rightarrow 0$  after the hold time

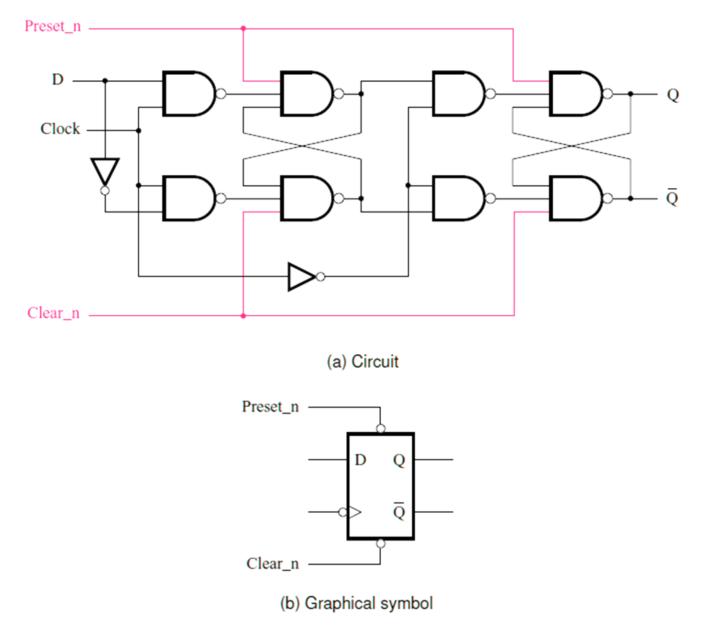

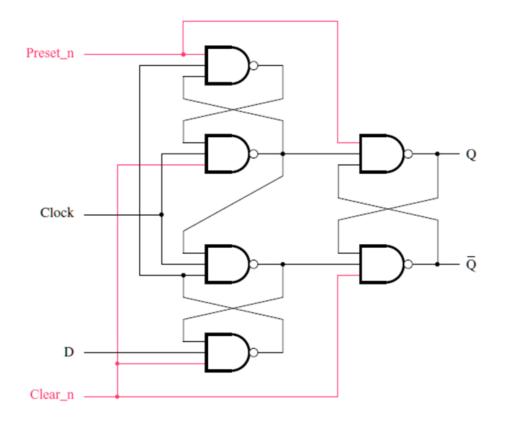

Figure 5.12. Master-slave D flip-flop with *Clear* and *Preset*.

Figure 5.13. Positive-edgetriggered D flip-flop with *Clear* and *Preset*.

(b) Graphical symbol

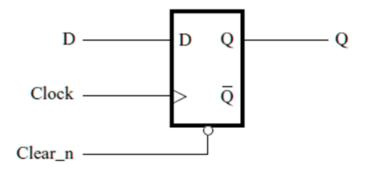

(a) D flip-flop with asynchronous clear

Figure 5.14. Timing for a flip-flop.

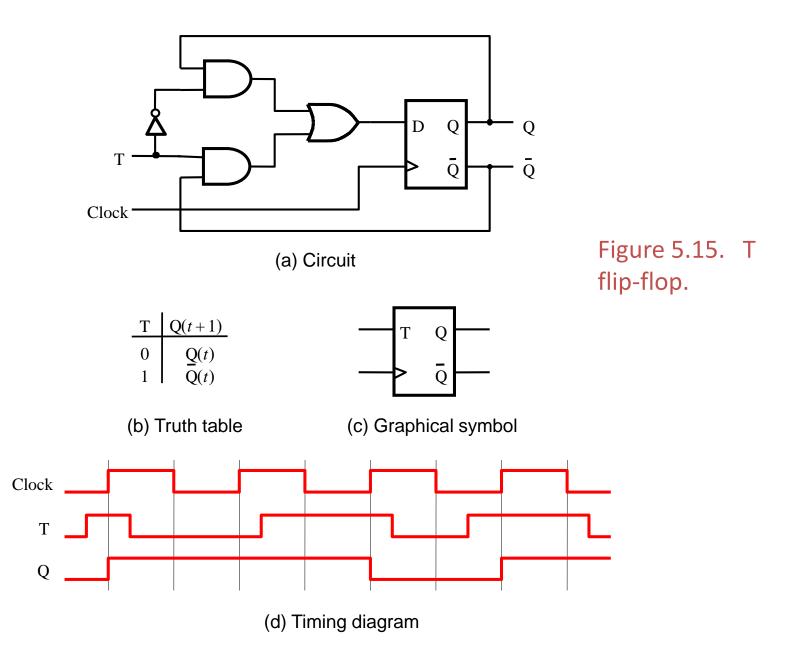

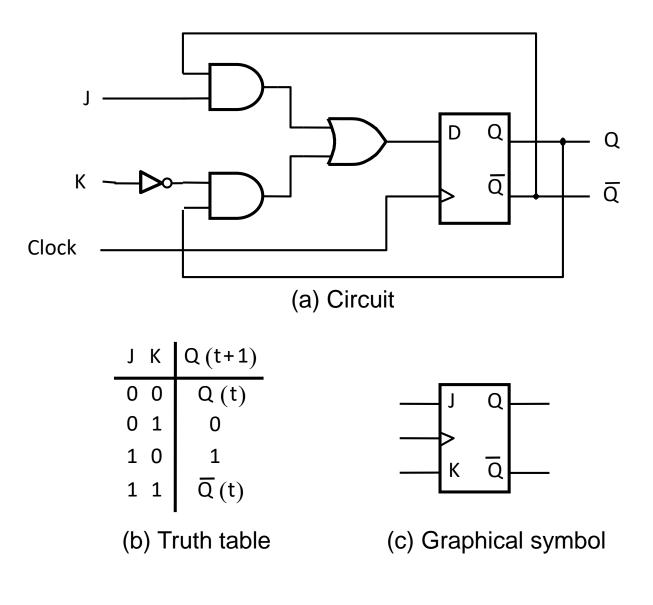

Figure 5.16. JK flip-flop.

(a) Circuit

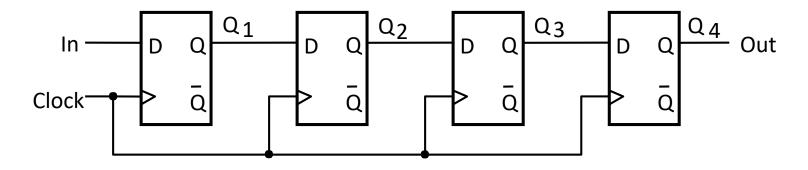

|                | In | Q <sub>1</sub> | Q <sub>2</sub> | Q3 | Q <sub>4</sub> = Out |

|----------------|----|----------------|----------------|----|----------------------|

| t <sub>0</sub> | 1  | 0              | 0              | 0  | 0                    |

| t <sub>1</sub> | 0  | 1              | 0              | 0  | 0                    |

| t <sub>2</sub> | 1  | 0              | 1              | 0  | 0                    |

| t <sub>3</sub> | 1  | 1              | 0              | 1  | 0                    |

| t <sub>4</sub> | 1  | 1              | 1              | 0  | 1                    |

| t <sub>5</sub> | 0  | 1              | 1              | 1  | 0                    |

| <sup>t</sup> 6 | 0  | 0              | 1              | 1  | 1                    |

| t <sub>7</sub> | 0  | 0              | 0              | 1  | 1                    |

(b) A sample sequence Figure 5.17. A simple shift register.